|

6/17/2023 0 Comments 100 mhz clock mini zed

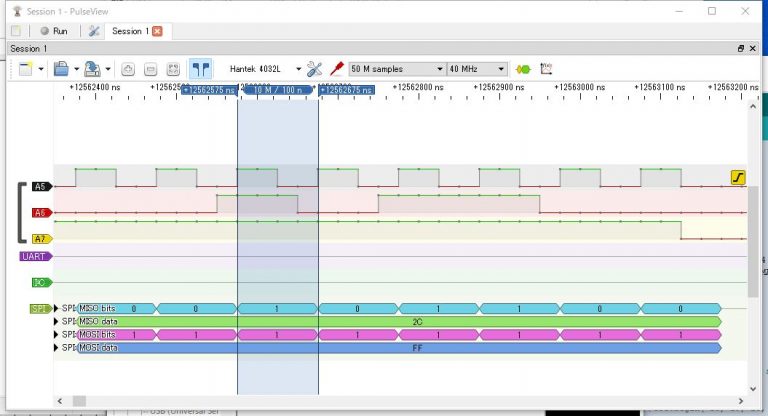

Zynq PS Clock System Block Diagram, Source: Zynq TRM, Copyright: Xilinx, Inc This clock drives an elaborate clocking hardware inside the Zynq SoC as shown in the image below: The 33.33MHz clock on Styx module is connected to the hard-silicon part of Zynq SoC at Pin location F7 (on CLG484 package) named PS_CLK (Processing System Clock). Xilinx Vivado Design Suite 2016.1 or higher.This article assumes you have access to the following: In this article, we will see how to generate a 100MHz clock from the PS (Processing System) section of Zynq and use in FPGA fabric. The Programmable Logic (PL) section of Zynq can also source a total of 4 different clocks from this clocking hardware. The 33.33MHz clock is connected to the hard-silicon part of Zynq SoC and drives different PLLs from which all clocks for the SoC core and its peripherals are derived.

On the other hand, Styx has a quite different clocking mechanism due to which we cannot directly assign a clock pin location in user constraints file. On Saturn, the clock is directly connected to FPGA’s GCLK pin allowing for the designs to directly use the clock by specifying the clock’s location in the user constraints file. One difference between Saturn vs Styx which one might notice is in the clock oscillators of both modules: Saturn has 100MHz clock oscillator whereas Styx has 33.33MHz clock oscillator. Styx Zynq Module comes in the same form factor as our Saturn Spartan 6 FPGA Module and so allows for a seamless upgrade in most cases.

The unique feature of Zynq-7000 series is that they are complete System on Chip (SoC) with an FPGA die which makes it a very powerful combination. Styx Zynq Module features a Zynq 7020 from Xilinx in CLG484 package.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed